Gate-All-Around Si Nanowire Transistors (SNWTs) for Extreme Scaling: Fabrication, Characterization and Analysis

#### Ru Huang Peking University (PKU) Beijing 100871, China

# Outline

- Introduction

- Fabrication and integration

- Recent advances in understanding SNWTs

- Parasitic effects

- Self-heating effects

- Variability

- Recent nanowire circuit demonstrations

- Summary

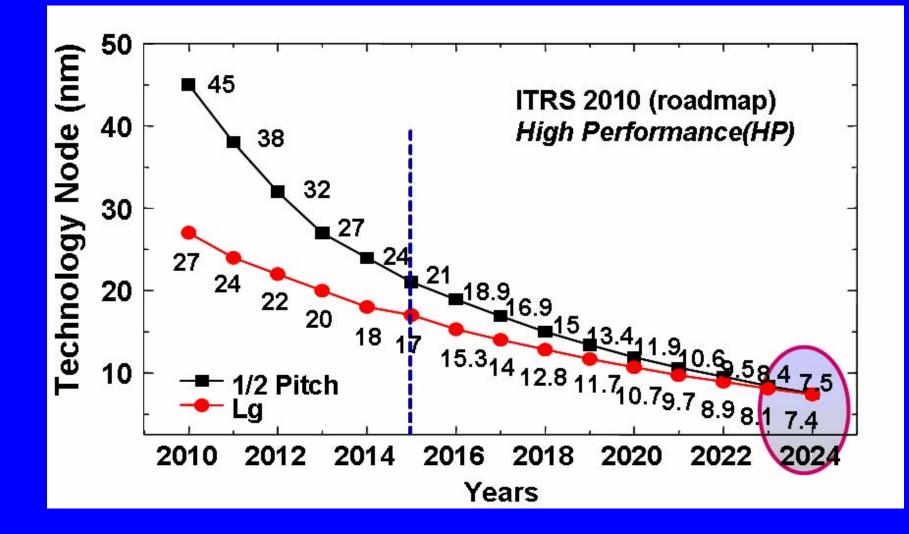

## **Introduction - 1/5**

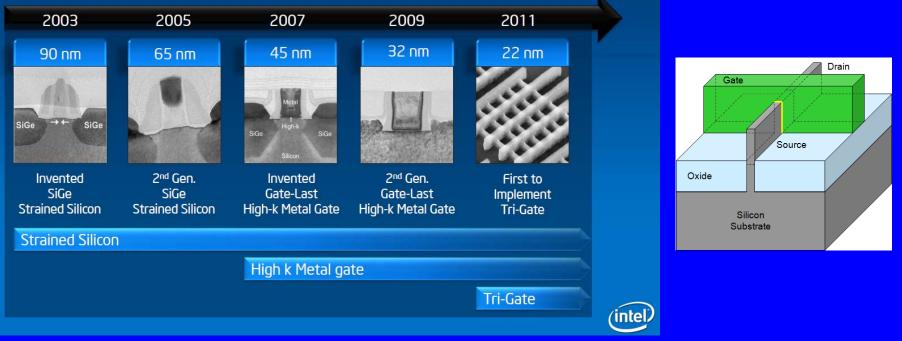

## Introduction - 2/5 We are entering the multi-gate era!

#### Intel's 22nm is Tri-gate transistor

#### Transistor Innovations Enable Technology Cadence

Source: M. Bohr and K. Mistry, http://www.intel.com

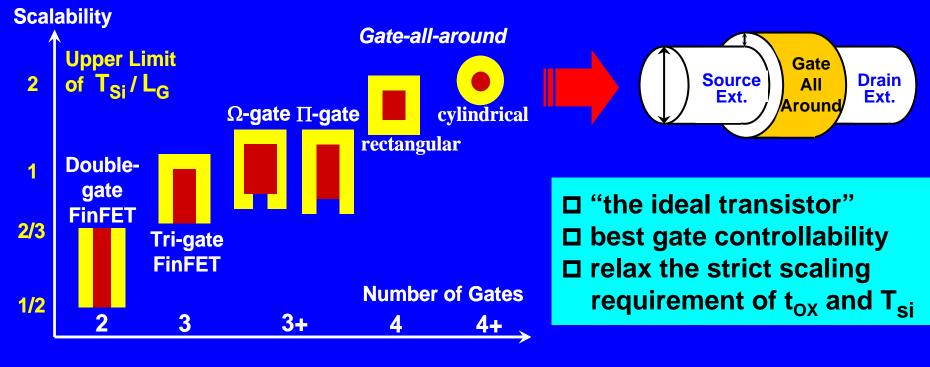

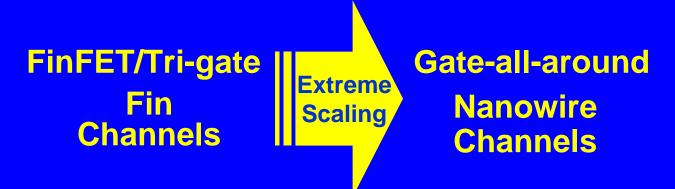

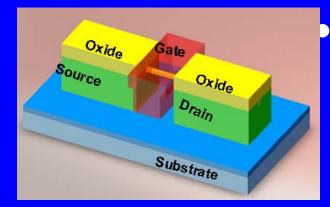

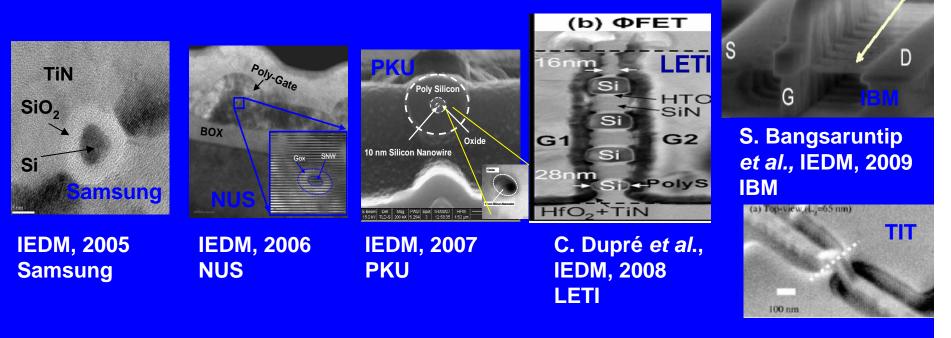

## Introduction - 3/5 Next: Gate-all-around Nanowire Transistor

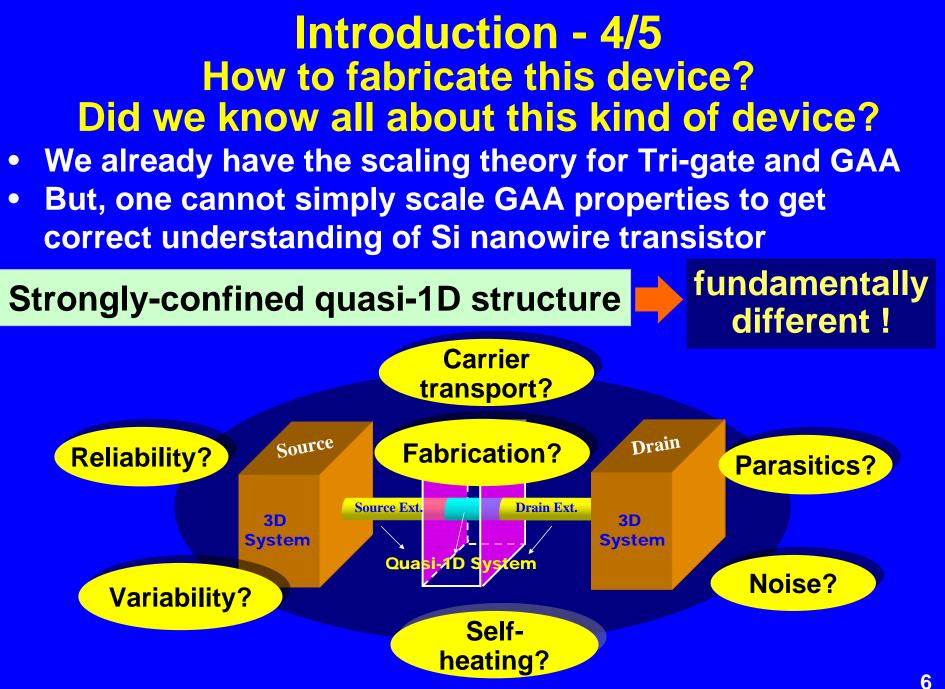

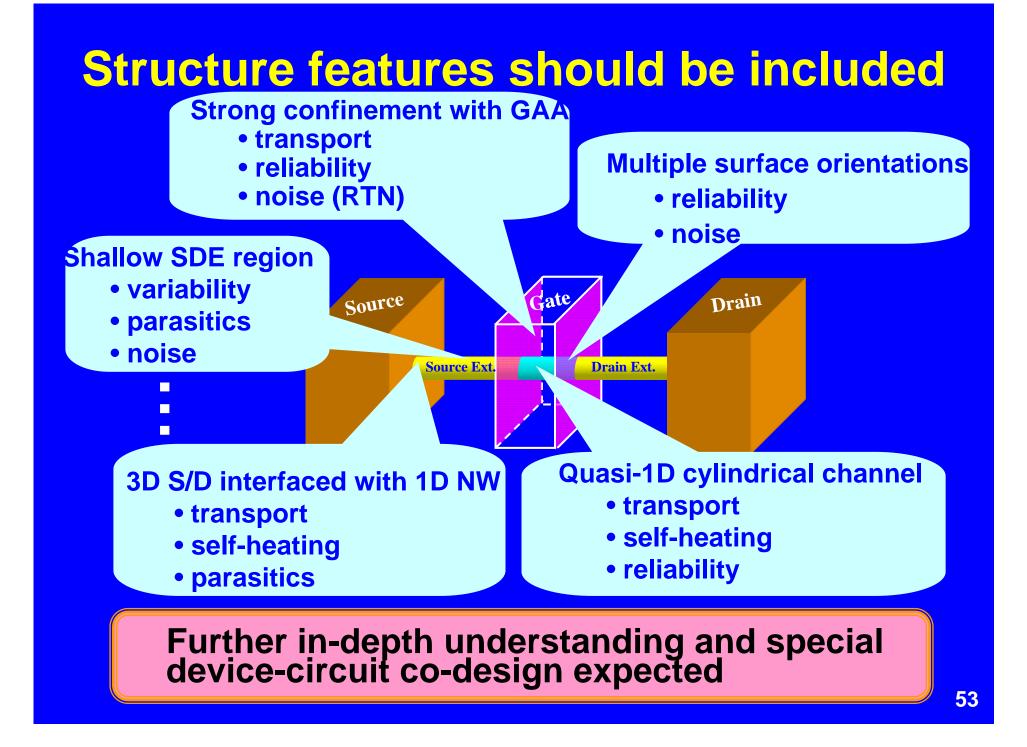

#### **Introduction - 5/5**

- Fabricate this device from top-down approach

Evaluate the key device characteristics for circuit applications with confined quasi-1D structure

- clarify the related physics

- find the challenges for optimization

- new characterizing techniques

- Fabrication and integration: *almost Manufacturable*

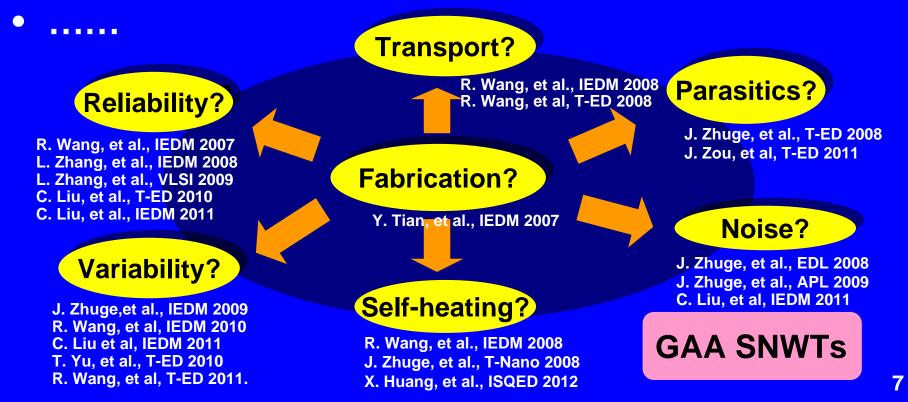

- Recent advances in understanding SNWTs

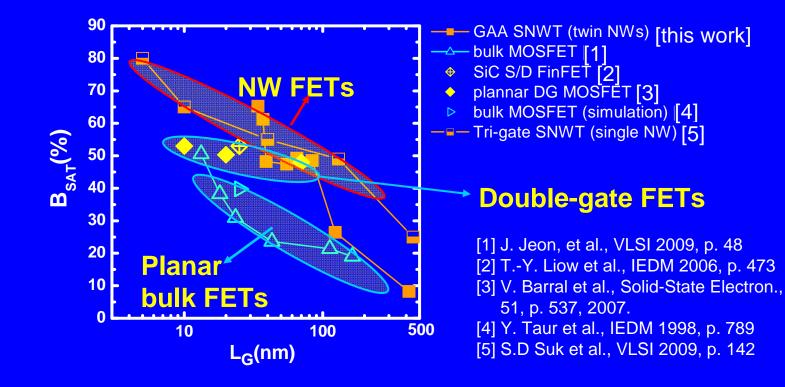

Intrinsic carrier transport: near-ballistic transport

- Fabrication and integration: almost Manufacturable

- Recent advances in understanding SNWTs

- Intrinsic carrier transport: near-ballistic transport

Better B<sub>SAT</sub> than planar and double-gate devices

- Fabrication and integration: almost Manufacturable

- Recent advances in understanding SNWTs

- Intrinsic carrier transport: near-ballistic transport

- Low-frequency noise: slightly degraded and fluctuated

- Parasitic effects (R and C): should be optimized

- Self-heating effects: observable when d<sub>NW</sub><14nm</li>

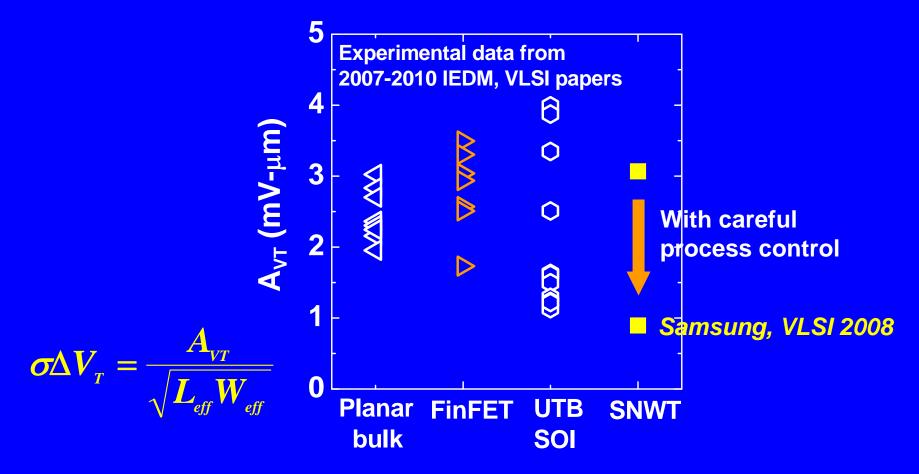

- Variability: holds the record low (static) variations

- Reliability: HCl is OK, but NBTI needs more studies

- Recent nanowire circuit demonstrations: On the way

SRAM, ring oscillator, current mirror...

- Other benefits for 3D integration, MtM applications...

- Summary: We are facing a great opportunity!

- Fabrication and integration: almost Manufacturable

- Recent advances in understanding SNWTs

- Intrinsic carrier transport: near-ballistic transport

- Low-frequency noise: slightly degraded and fluctuated

- Parasitic effects (R and C): should be optimized

- Self-heating effects: observable when d<sub>NW</sub><14nm</li>

- Variability: holds the record low (static) variations

Reliability: HCl is OK, but NBTI needs more studies

- Recent nanowire circuit demonstrations: On the way

SRAM, ring oscillator, current mirror...

- Other benefits for 3D integration, MtM applications...

- Summary: We are facing a great opportunity!

# Outline

#### Introduction

#### Fabrication and integration

- based on bulk (our focus)

- based on SOI

- with stacked NW channel

- Recent advances in understanding SNWTs

- Parasitic effects

- Self-heating effects

- Variability

- Recent nanowire circuit demonstrations

- Summary

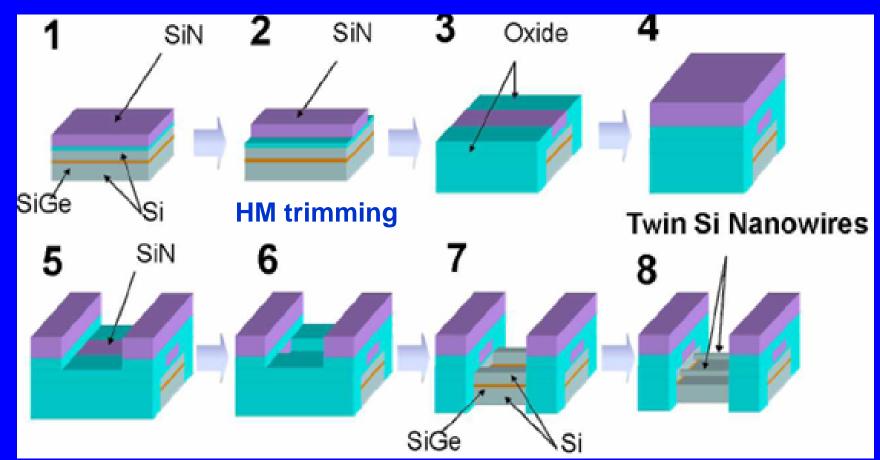

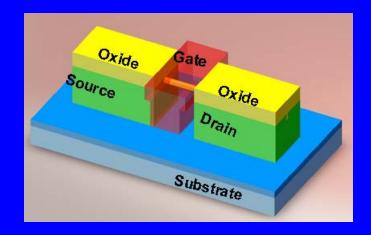

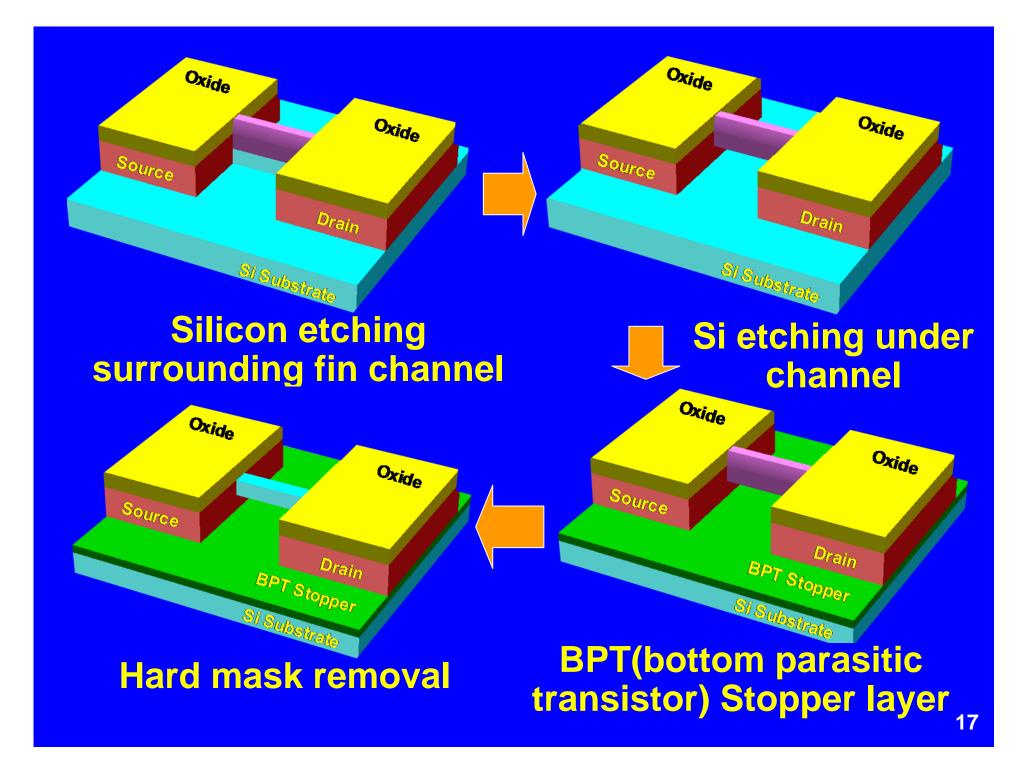

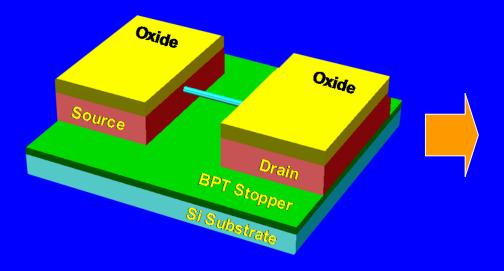

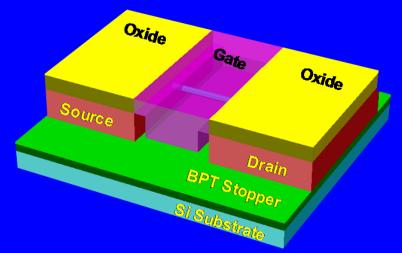

## **Top-down process for SNWTs**

#### **Key points**

- NW formation

- NW releasing or suspending

Sato S, et al., SSE, 2010, TIT

NW

## **Bulk SNWTs - Samsung method**

✓ HM Trimming for NW definition

✓ SiGe/Si stack epi for releasing

diameter = 10nm t<sub>ox</sub>=3.5nm TiN metal-gate

S.D.Suk et al., IEDM, 2005

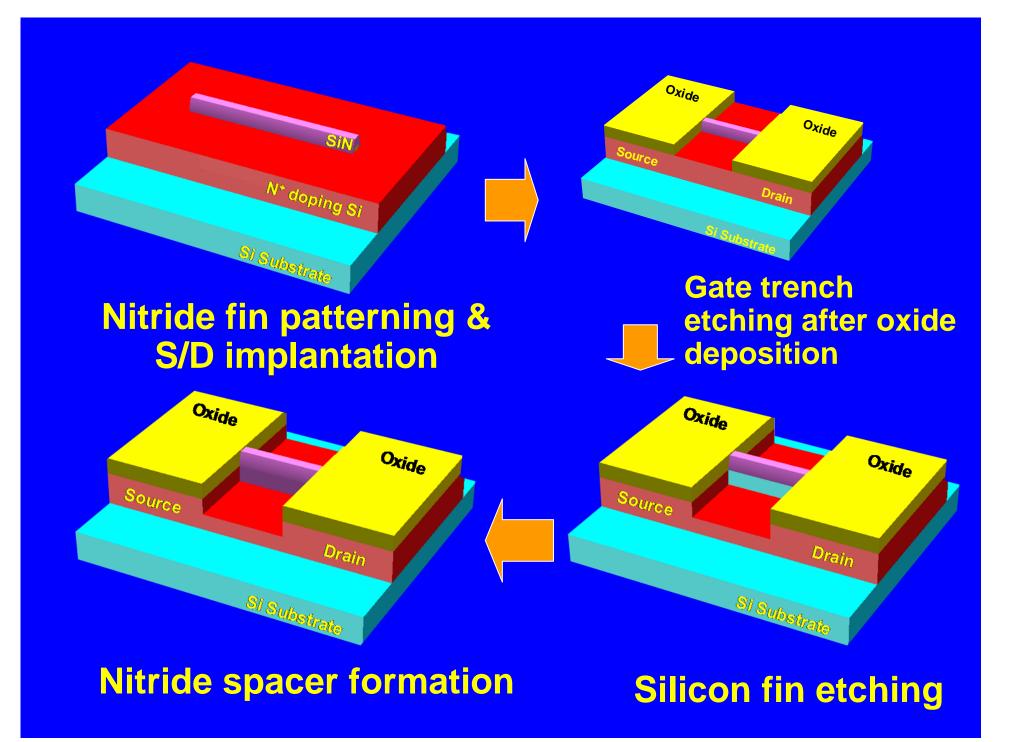

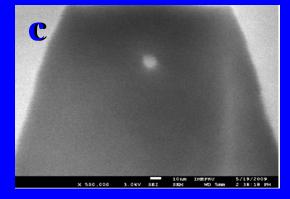

#### Self-aligned bulk SNWTs by epifree compatible process

based on bulk substrate

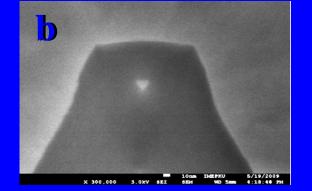

NW originally defined by e-beam, thinning and cylinder channel shaping by self-limiting oxidation and annealing

NW released by isotropic otch with HM

NW released by isotropic etch with HM

Y. Tian et al., IEDM, 2007, PKU

**Cylindrical shaping**

# Gate oxidation & Poly-Si gate formation

- diameter = 10nm

- t<sub>ox</sub>=5nm

- Poly gate

#### **NW formation**

#### NW shaping and diameter controlling

**Patterning for**

**Oxidation** Patterning for original channel + (Temperature & time)

> **Traded with Oxidation** retardation effect

#### **Increasing oxidation time: from triangle to circle**

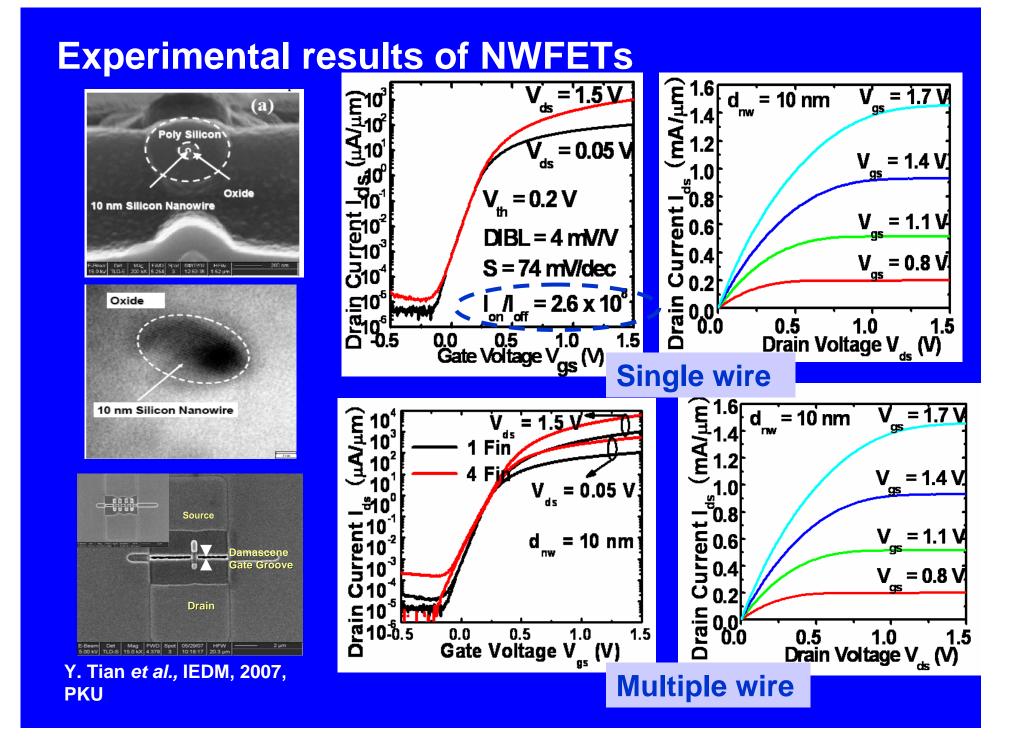

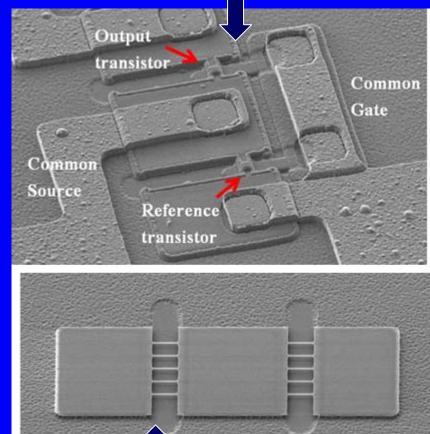

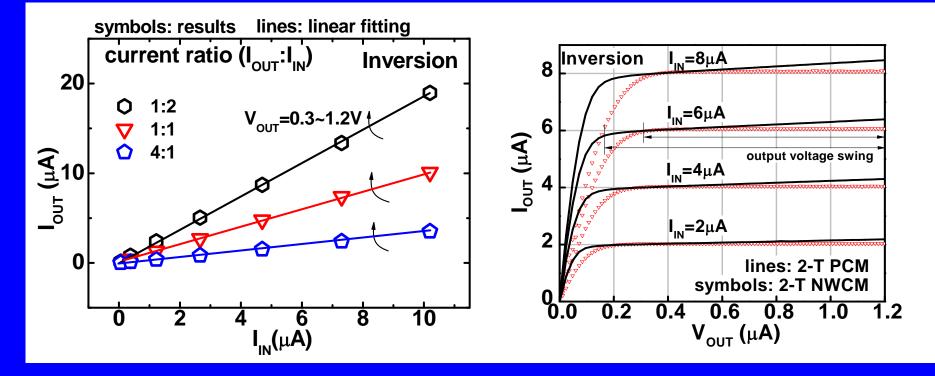

#### Current mirror (CM) based on SNWTs Single NW

#### R.Huang et al., T-ED, 2011, Pl

Multi NW adjust current ratio with NW number

#### **Testing results**

$OVC(\%) = 100(\Delta I_{OUT}/I_{OUT})/\Delta V_{OUT}$

| OVC     | NW CM         | Planar CM   |

|---------|---------------|-------------|

| 2T      | ~ <b>0.2%</b> | $\sim$ 5.7% |

| cascade | $\sim$ 0.05%  | $\sim$ 1%   |

# Outline

- Recent advances in understanding SNWTs

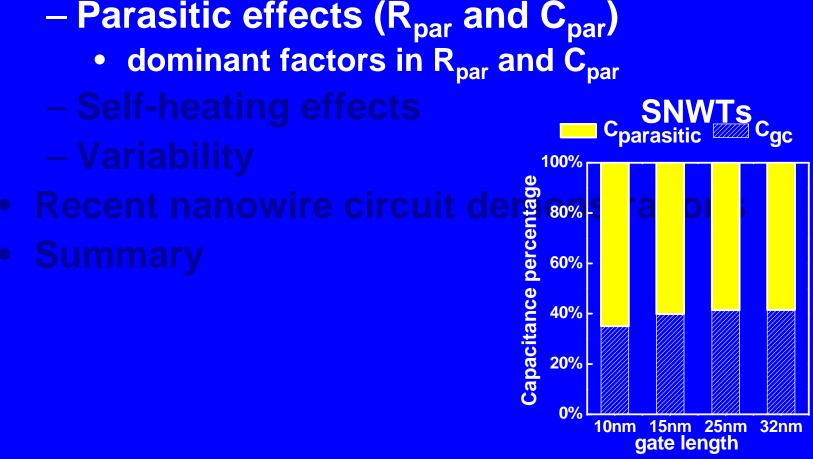

- Parasitic effects (R<sub>par</sub> and C<sub>par</sub>)

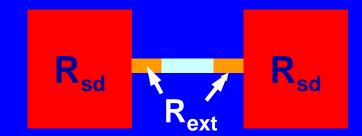

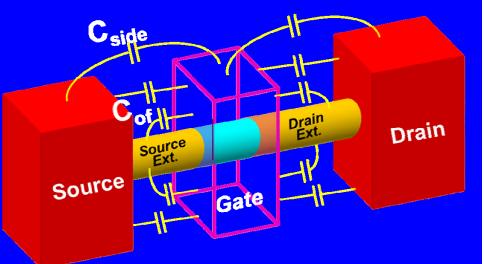

#### **Parasitic R and C in GAA SNWTs**

- SNWT is worse than planar devices and FinFETs

- larger and dominant SDE series resistances

- larger outer fringing capacitances

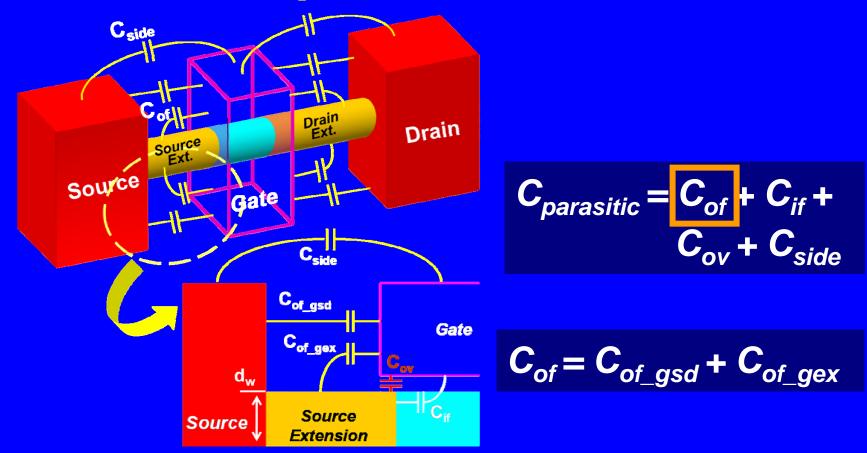

## Parasitic capacitances in SNWTs

A predictive model for parasitic C in SNWTs has been developed\*

\*Jibin Zou et al., T-ED, vol. 58, no. 10, Oct. 2011, PKU

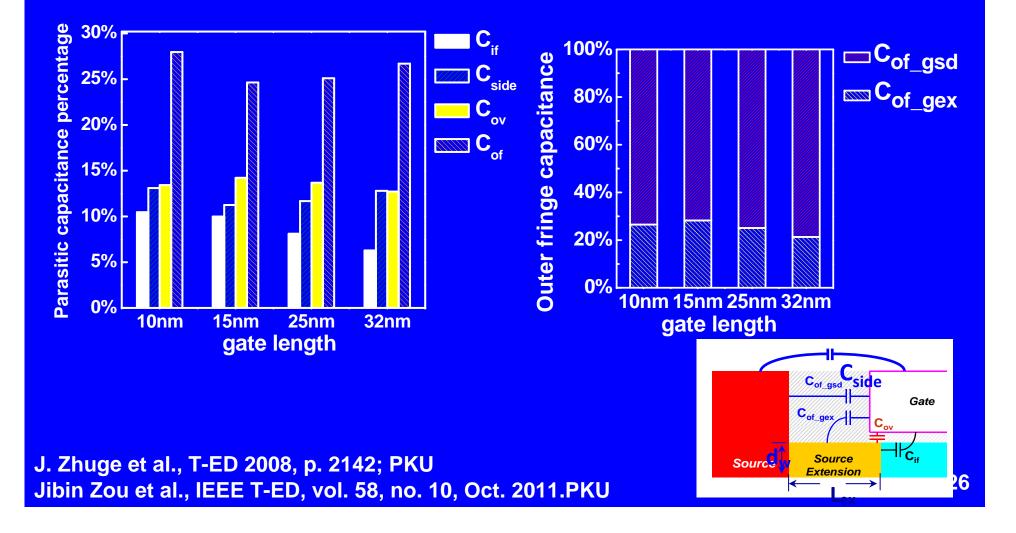

## Impacts of parasitic C -1/2 • Outer fringe capacitance $C_{of}$ is dominant $-C_{of_gsd}$ is the main contributor

#### Key messages for design optimization of parasitics in SNWTs

- multi-wire structure is needed

with merged SDE structure

- gate height need to be reduced

- Optimizations in SDE regions

- different from DG FinFETs

- FinFETs: underlap is better

- SNWTs: overlap is better

- due to better gate control capability in SNWTs

- can effectively reduce R<sub>ext</sub> but with smaller impact on

- C<sub>parastic</sub>

# Outline

- Introduction

- Fabrication and integration

- Recent advances in understanding SNWTs

- Parasitic effects (R and C)

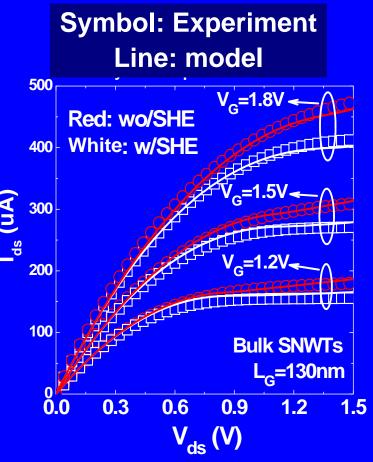

- Self-heating effects (SHE)

- Variability

- Recent nanowire circuit demonstrations

- Summary

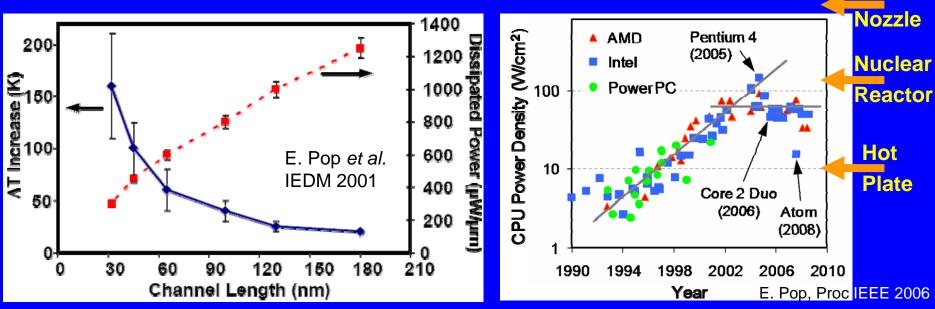

## Transistor thermal challenges at nanoscale -1/2

. . . . . .

Increasing self-heating with size shrinking  Headache for analog circuits

mismatch issue due to thermal distribution

Reliability: NBTI ...

Thermal noise Rocket

## Transistor thermal challenges at nanoscale -2/2

Worse SHE for scaled technology: Confined geometries (thin Si films in UTB, DG...) and novel materials (SiGe, Ge, silicide...) with poor thermal conductivity

| Material         | k <sub>th</sub> (₩/mK) | IBM                             | Gate         |  |

|------------------|------------------------|---------------------------------|--------------|--|

| Si               | 148                    |                                 |              |  |

| Ge               | 60                     | Strained                        |              |  |

| Silicides        | 40                     | Silicon                         | Source Drain |  |

| Si (10 nm)       | 13                     | Silicon-germanium               | FinFET       |  |

| SiO <sub>2</sub> | 1.4                    | E. Pop <i>, Proc. IEEE</i> 2006 |              |  |

• SNWTs: more confined structure So, how about the self-heating?

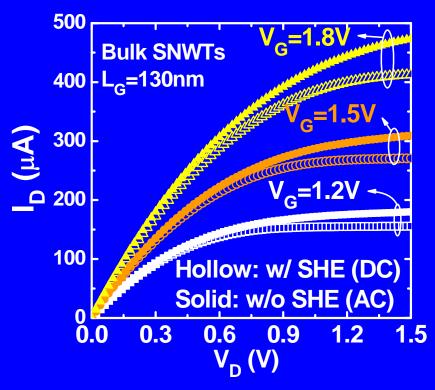

## **SHE Characterization of SNWTs**

#### AC conductance method

#### SNWTs on fully bulk substrate (w/o e-SiGe S/D or SOI)

R. Wang, et al., IEDM 2008, PKU

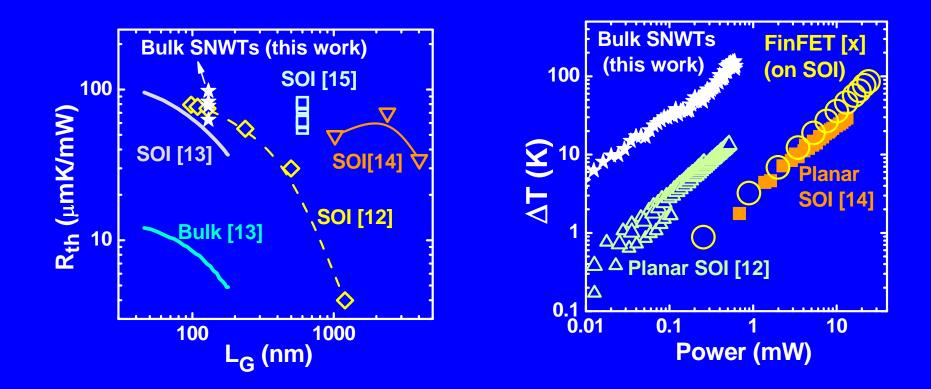

# Comparisons

#### SHE in SNWTs even on bulk-Si substrate is a little bit worse than SOI devices

[12] G. Guegan et al., *Mater. Res. Soc. Symp. Proc.*, 2006; [13] K. Etessam-Yazdani et al., *ITHERM*, 2006; [14] B. M. Tenbroek et al., *IEEE TED*, 1996; [15] W. Jin et al., *IEDM*, 1999; [x] A.J. Scholten et al., IEDM 2009.

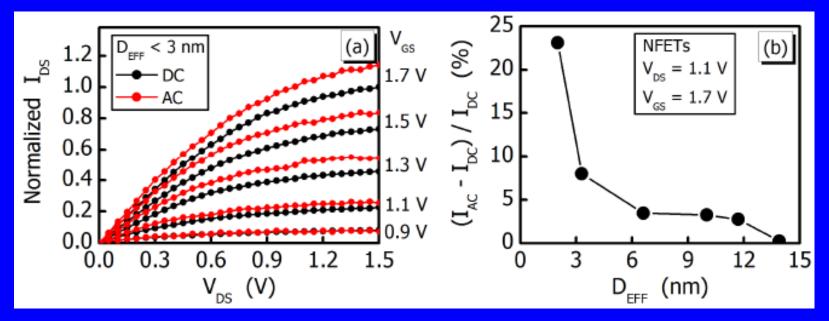

# Improvement by increasing heat dissipation through the gate stack?

- High-k gate dielectric has better thermal conductivity than SiO<sub>2</sub> or SiON gate material

- but still have non-negligible SHE when d<sub>NW</sub> < 14nm</li>

HfO<sub>x</sub> / TaN gate, L<sub>G</sub>=21nm

S. Bangsaruntip, et al., VLSI 2033

## Why degraded SHE in SNWTs?

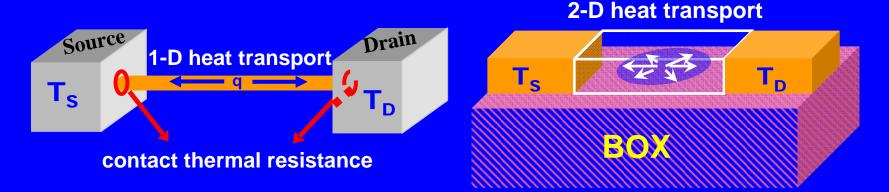

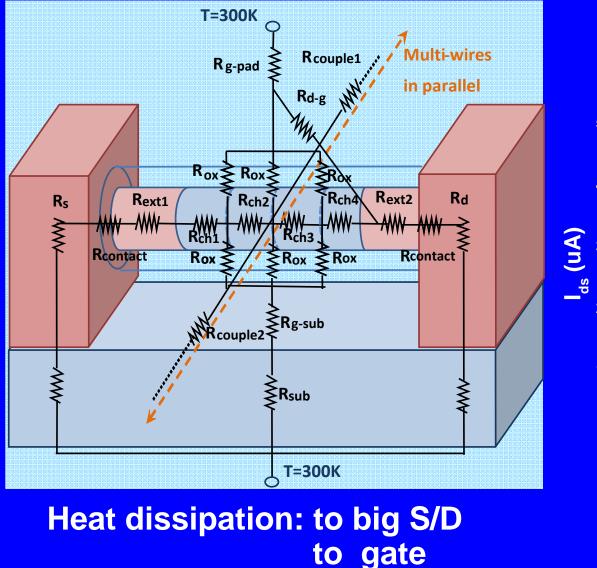

1D heat transport for strongly-confined NW structure

limited modes for heat dissipation

# Why degraded SHE in SNWTs?

1D heat transport for strongly-confined NW structure

limited modes for heat dissipation

- Additional contact thermal resistance

- abrupt interface between 1D-NW and 3D-S/D region

- does not exist in planar devices

- GAA: increased surface/volume ratio, strong phononboundary scattering and thus increased boundary R<sub>th</sub>

– worse than UTB SOI, DG/TG structures

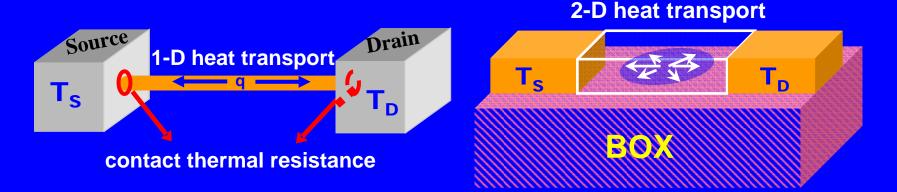

#### Thermal conductivity model for Si NWs

[a] A. I. Hochbaum et al., Nature, vol. 451, p.163, 2008.

[b] D. Li et al., APL, vol. 83, p. 2934, 2003.

[c] P. Martin et al., PRL, vol. 102, p. 125503, 2009.

X. Huang, et al., to be published.

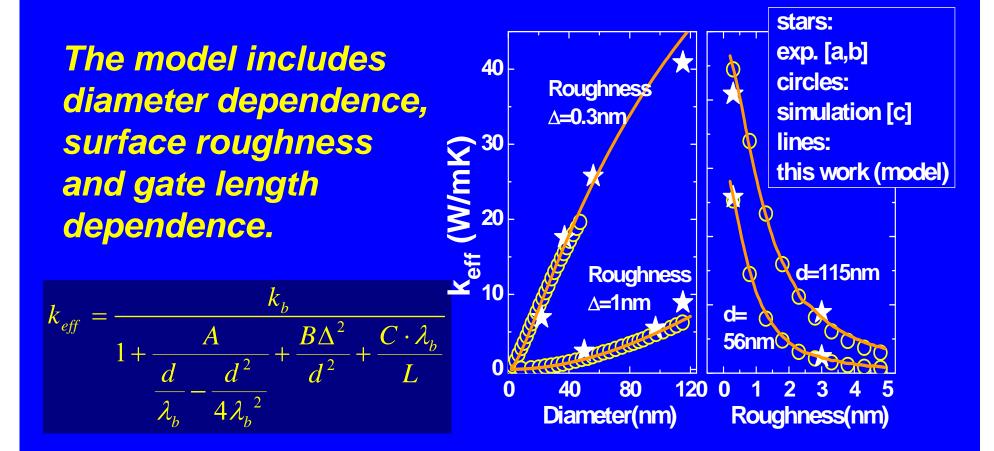

#### **Equivalent Thermal Network for SNWTs**

X. Huang, et al., to be published.

# Outline

- Fabrication and integration (a quick review)

- Recent advances in understanding SNWTs

- Intrinsic carrier transport

- Parasitic effects (R and C)

- Low-frequency noise

- Self-heating effects

- Variability

- Recent nanowire circuit demonstrations

- Summary

#### *"There's plenty of room at the bottom" -- Richard P. Feynman* **"There's also plenty of noise** and *variation* at the bottom..."

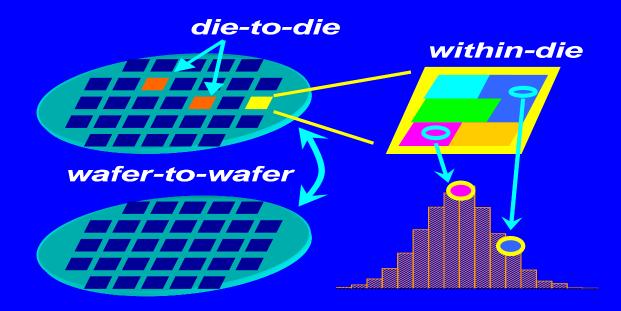

- Variability challenges in nano-CMOS

- new process technologies

- new materials

- much smaller devices

## Variation in nano-scale devices

| Systematic | OPC, Layout Dependent Strain                                                         |

|------------|--------------------------------------------------------------------------------------|

| Random     | Random Dopants, Line Edge<br>Roughness, High-k Morphology,<br>Metal Gate Granularity |

- Random variations near atomic dimensions

impacts circuit functionality and stability

- New architecture NWFET with ultra-scaled dimension and surrounding gate structure

*What about its variability?*

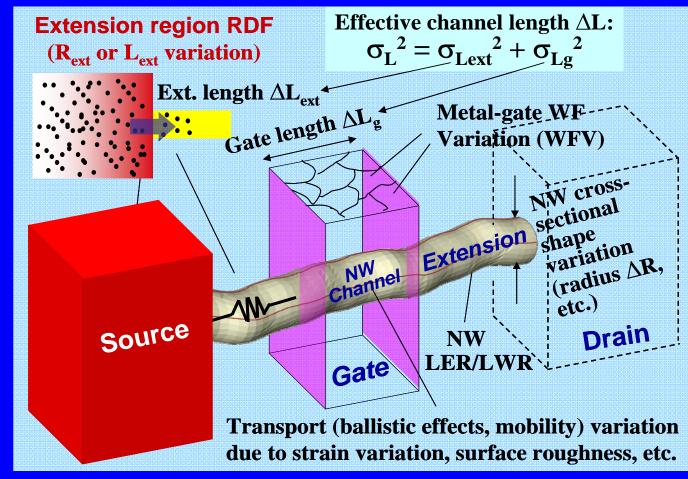

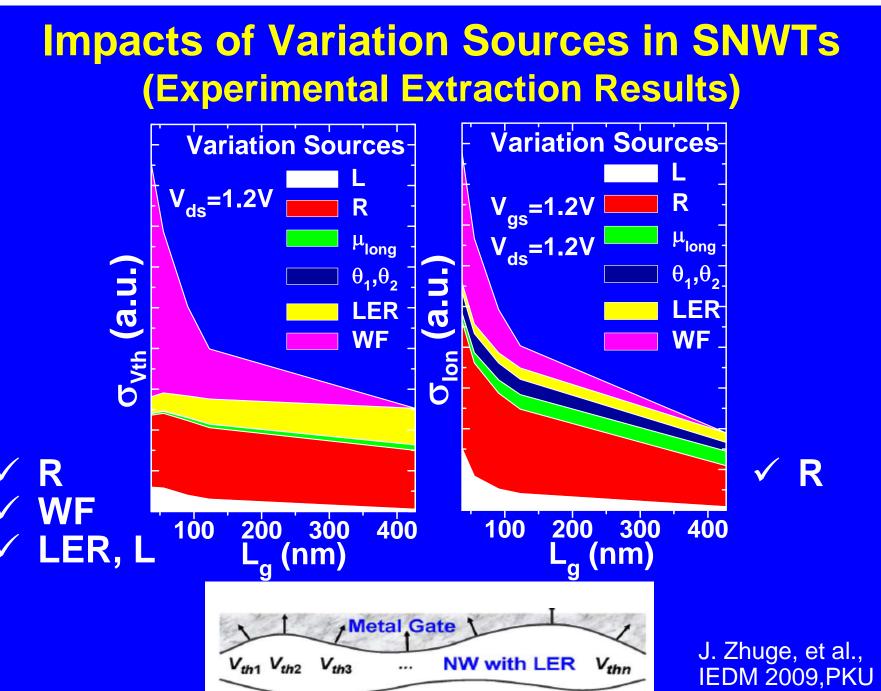

## What about GAA nanowire MOSFETs?

Elimination of random dopant fluctuation (RDF) in the channel, what about other sources?

#### New sources: ✓ diameter variation, NW LER/LWR, NW SDE RDF

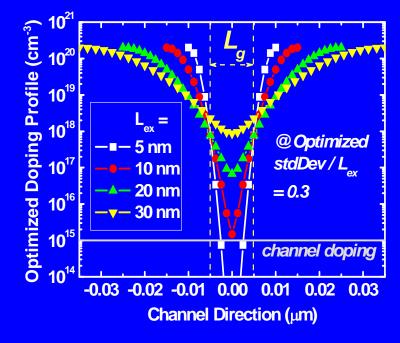

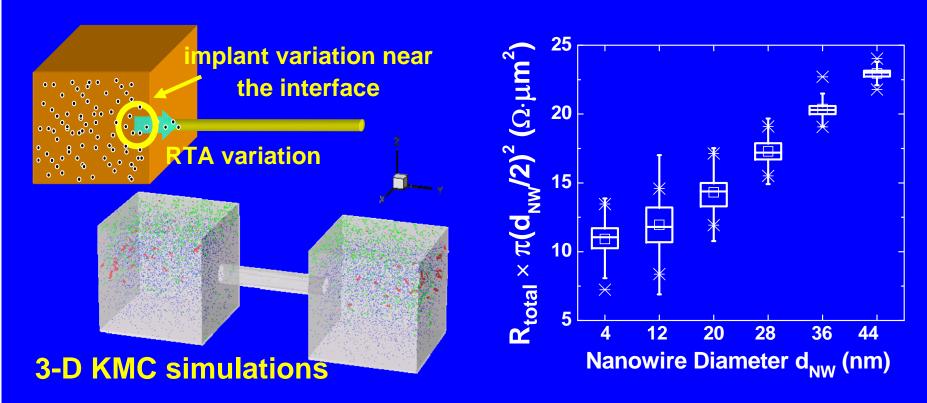

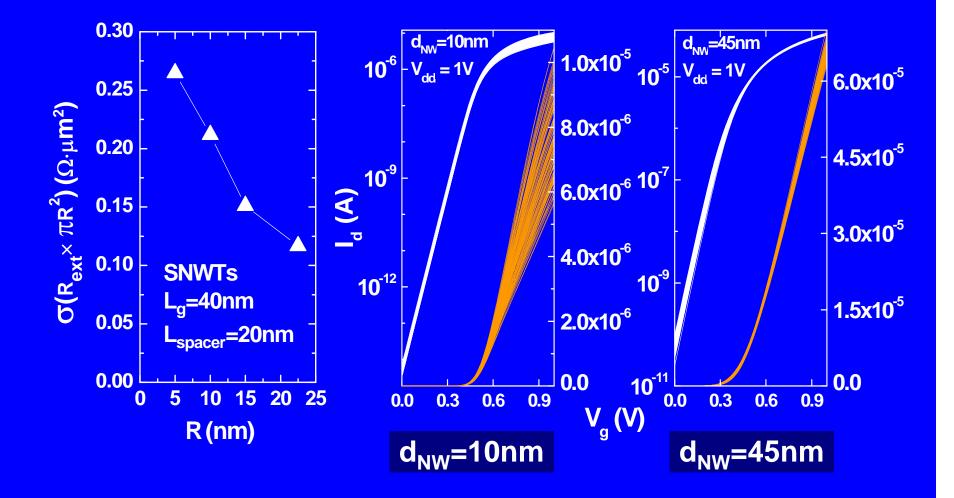

## **Discussion - 1/2: SDE RDF (1)**

- Diameter-Dependent Annealing (DDA): thinner NW results in faster diffusion

- Rext reduction and variation

- Leff reduction and variation

#### **Discussion - 2/2: SDE RDF (2)**

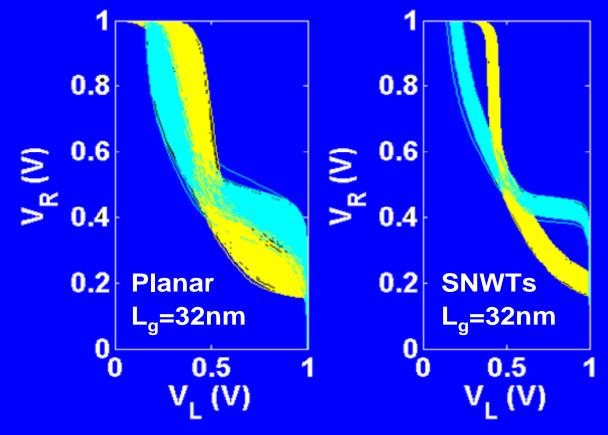

#### SNWT vs. planar MOSFET – Simulations -1/2

SNWT-based SRAM cells

Larger NM and less variation of noise margin

intrinsic channel and excellent SCE-suppression

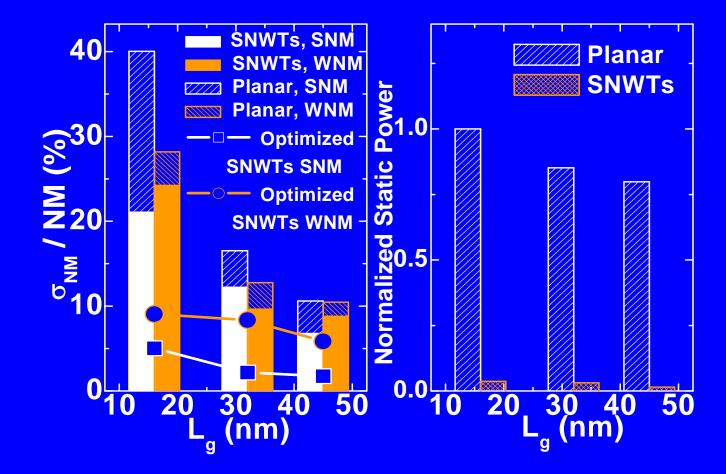

#### SNWT vs. planar MOSFET – Simulations -2/2

Scaled SNWT-based SRAM cells

Less NM variation and much less static power consumption

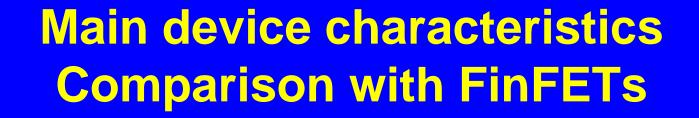

# Comparisons with FinFET and UTB SOI Devices

Experimental demonstrations so far

First-order device-level comparisons with FinFETs

# Outline

- Introduction

- Fabrication and integration

- Recent advances in understanding SNWTs

- Parasitic effects

- Self-heating effects

- Variability

- Recent nanowire circuit demonstrations

- Summary

# **Circuit demonstration is at early stage**

TSNWFET

0.6 0.8 1.0 1.2

V\_(V)

lanar SRAM

SRAM

400

300

100

<sup>300</sup>/۳/۳ MNS

- SRAM (Samsung, VLSI 08)

- Larger SNM than planar and **FinFET devices**

- Smallest variation demo

- Current Mirror (Peking Univ., T-ED 11)

- Good performance in both inversion and subthreshold regions

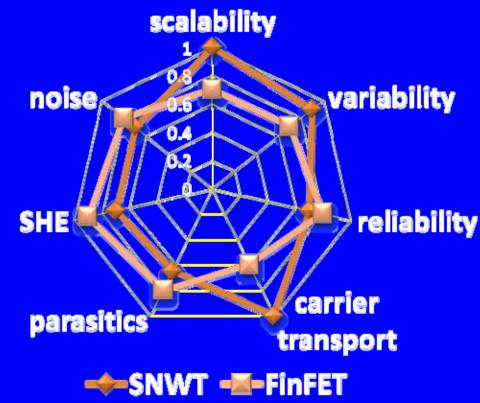

- 25-Stage Ring Oscillators (IBM, VLSI 10)

- $d_{NW} = 3 \sim 14 \text{ nm}, L_G = 25 \sim 55 \text{ nm}$

- Limited by the SDE series resistance, need further improvement

# Outline

- Introduction

- Fabrication and integration

- Recent advances in understanding SNWTs

- Parasitic effects

- Self-heating effects

- Variability

- Recent nanowire circuit demonstrations

- Summary

#### Key Messages for GAA SNWTs: Summary

- Almost manufacturable: but still needs better process controllability

- Variability: lowest (static) variations

- key variation sources for further optimization: diameter variation, WFV, NW LER, SDE RDF

- **?** Relatively severe parasitic effects

- ? Non-negligible SHE even on bulk: thermal balanced design needed

- ? Circuit demonstration: still on the way

# Thank You Very Much!